基于FPGA的無線射頻讀卡器開發與設計

文章出處:http://www.xujuanpiju.com 作者:Niladri Roy 人氣: 發表時間:2011年10月23日

與其他常用的自動識別技術如條形碼和磁條一樣,無線射頻識別(RFID)技術也是一種自動識別技術。每一個目標對象在射頻讀卡器中對應唯一的電子識別碼(UID),或者“電子標簽”。標簽附著在物體上標識目標對象,如紙箱、貨盤或包裝箱等。射頻讀卡器(應答器)從電子標簽上讀取識別碼。

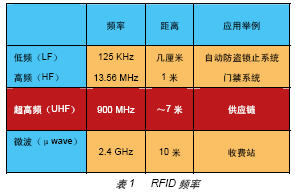

基本的RFID系統由三部分組成:天線或線圈、帶RFID解碼器的收發器和RFID電子標簽(每個標簽具有唯一的電子識別碼)。表1顯示了常用的四個RFID頻率及其潛在的應用領域。其中,目前商業上應用最廣的是超高頻(UHF),它在供應鏈管理中有可能得到廣泛的應用。

EPC電子標簽

EPC表示電子產品代碼,是RFID電子標簽的標準,它包括電子標簽的數據內容和無線通信協議。EPC標準將條形碼規范中的數據信息標準與ANSI或其他標準化組織(802.11b)制定的無線數據通信標準結合在一起。目前應用在供應鏈管理中的EPC標準,屬于第二代EPC Class-1標準。

Class-1標簽在出廠時已經被寫入,但也是可以現場下載。通常情況下,一旦標簽已被寫入,內存即被鎖定不可再次寫入信息。Class-1標簽采用常規的分組傳輸協議—讀卡器發送包含相關命令和數據的數據包,標簽隨后做出響應。

惡劣的讀卡器應用環境

RFID的應用環境可能非常惡劣。信道的工作頻率是免許可的工業、科技與醫藥(ISM)頻帶。此頻帶中的RFID讀卡器受到來自無繩電話、無線耳麥、無線數據網絡以及其他臨近讀卡器的干擾。必須將每一讀卡器的RF接收器前端設計為能夠抵御強干擾信號,避免產生可導致詢問錯誤的失真。接收器的噪聲必須保持在較低的水平,以便具備足夠的動態范圍,從而以無錯方式檢測出低電平標簽響應信號。

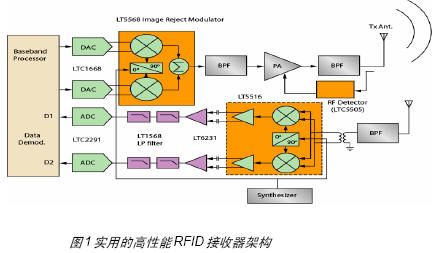

圖1中所示的讀卡器RF射頻收發器,是一個成熟的設計,能夠在存在大量干擾源的惡劣環境中穩定地工作。發射器和接收器都帶有一個高動態范圍直接轉換調制器和解調器,因此最大限度地提高了穩定性并降低了成本。

實用和可靠的射頻接收器設計

接收器的核心是Linear公司的LT5516,這是一種高度集成化的直接轉換正交解調器,芯片上提供了一個精確正交移相器(0度至90度)。來自天線的信號在通過射頻濾波器之后,通過一個不平衡變壓器直接輸入到解調器輸入端口。由于LT5516的噪聲系數很低,在不需要低噪放大器(LNA)的情況下,仍能保持其21.5dBm IIP3和9.7dB P1dB的性能。

在接收數據時,讀卡器發射連續載波(未調制),以便為標簽提供電源。在收到請求后,電子標簽通過對載波進行調幅,響應一個碼流。所采用的調制方式為幅移鍵控(ASK)或者反相-幅移鍵控鍵控(PR-ASK)。解調器帶有兩個正交移相檢出式輸出端口,因此具備天然的分集接收功能。如果由于多路或相位取消導致某個通道無法接收信號,另一條通道(移相90度)就可接收較強的信號,反之亦然。這樣,整體接收可靠性就得以提高。

一旦解調完成,即可將I(相內)和Q(正交相位)差分輸出信號以AC方式耦合至一個運算放大器(被配置為一個差分放大器),隨后被轉換為單端輸出信號。這個時候應將高通角頻率設置為5KHz,低于接收數據流的最小信號頻率,高于最大多普勒頻率(可能被運動標簽采用),同時保持高于電力線頻率(60Hz)。這樣,輸出信號就能利用被配置為四階低通的LT1568順利穿過低通濾波器。低通角頻率應被設置為5MHz,以便最大碼流信號穿過濾波器,達到基帶。

基帶信號然后被一個雙路低功耗模數轉換器(LTC2291,分辨率為12位)進行數字化處理。由于標簽碼流的帶寬為5KHz至5MHz,LTC2291能夠以25MSps的速率進行充分的采樣,從而精確地捕獲解調信號。在需要的時候,還可在基帶DSP中實現額外的數字濾波。這樣,接收器就能具備最大的邏輯閾值設置靈活性,該設置可由基帶處理器以數字化方式執行。

基帶任務和數字化射頻信道化處理,可提高用全FPGA解決方案實現的吸引力和集成度。

高動態范圍射頻發射器設計

發射器集成了一個鏡像抑制直接轉換式調制器。LT5568具備很高的線性度和較低的背景噪聲,因此能夠為所發射的信號提供出色的動態范圍性能。調制器能夠從數模轉換器(DAC)接收正交式基帶I和Q信號,然后直接調制至900MHz發射頻率。

在內部,LO(本地振蕩器)被精確正交移相器分割。經調制的射頻信號被合并為一個單端、單邊帶射頻輸出信號(鏡像被抑制了46dBc)。此外,調制器還帶有匹配的I和Q混合器,從而最大限度地抑制了LO載波信號(至-43dBm)。

復合調制電路具備出色的鄰道功率比(ACPR),有助于滿足發射頻率屏蔽要求。例如,當調制器射頻輸出電平為-8dBm時,ACPR指標優于-60dBc。由于具備更出色的ACPR性能,信號可被放大至許可的1w功率(在美國為+30dBm),或者放大至2w,以符合歐盟規范。在上述兩種情況下,重要的是保持電平固定,因為該電平用于向電子標簽提供電源,并最大化讀卡距離。LTC5505型射頻功率檢測器的內部溫度補償功能,可準確地測定功率,提供穩定的反饋信號,以調節射頻功率放大器的輸出功率。

基帶處理和網絡接口

在基帶頻率上,FPGA執行發送至DAC和來自模數轉換器(ADC)的波形的信道化任務。這一過程也被稱為數字中頻處理,涉及濾波、增益控制、頻率轉換和采樣率變化等。FPGA甚至可以并行處理多個信道。

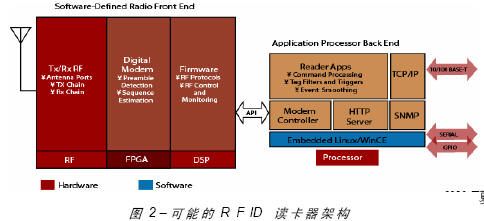

圖2顯示了一個射頻讀卡器的架構。其他基帶處理任務包括:

先導字段檢測

排序估計

調制和解調(ASK、頻移鍵控和相移鍵控)

信號產生

相關器處理

峰值檢測和閾值設定

CRC糾錯和校驗和

編碼和解碼(NRZ、Manchester、單極性、差分雙極性和Miller)

幀檢測

ID去擾

安全加密引擎

所收到的RFID標簽數據可通過串口或網絡接口被傳送至企業系統服務器。這種傳統的架構正逐步演變為一個高級分布式 TCP/IP 網絡的一個部分。在該網絡中,射頻讀卡器將負責管理臨近的標簽。在這種情況下,射頻讀卡器就象是電子標簽和連接至企業軟件系統的智化分布式數據庫之間的網關。

取決于硬件/軟件功能分區情況,這些基帶任務即可在FPGA上完成,也可在DSP上完成,或者由二者聯合執行。Xilinx公司推出了一個IP內核套件,其中包括FIR、CIC、DDS、DUC、DDC、比特相關器、正弦/余弦LUT等。這些邏輯電路非常適合執行加密引擎任務(加密引擎采用移位寄存器和XOR)。針對Xilinx® VirtexTM-4系列的DSP48引擎十分適合執行其他信號處理任務。

一個基帶處理器負責控制各種基帶處理任務的功能性和調度,還負責鏈路層協議。這些基帶處理任務包括跳頻、發送前偵聽、防沖突算法處理等。基帶處理器還提供了以太網、USB、固件等接口。

基帶任務和數字化射頻信道化處理,可提高全FPGA解決方案的吸引力和集成度。FGPA功能、DSP功能,以及基帶處理功能,都可被整合于一個帶有嵌入式處理器的FPGA。

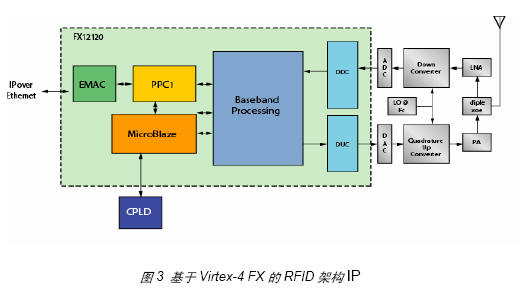

圖 3 顯示了一個基于 FPGA 的 RFID 處理器的架構。嵌入式處理器可以是一個硬核(譬如,Virtex-4 FX產品家族采用的PowerPCTM),還可以是一個軟核 (譬如SpartanTM設備中采用的MicroBlazeTM),甚至是PowerPC和MicroBlaze的結合體。用戶可以將內置硬以太網MAC(EMAC)連接至外部以太網物理層,進而連接至以太網。另外,用戶還可使用面向10/100-BaseT的Lite Ethernet MAC IP。

PowerPC/MicroBlaze 嵌入式處理器執行以下任務:

EPC數據處理

協議處理

詢問調度

TCP/IP 網絡接口

控制和監視

調制解調器控制

升級代理

HTTP服務器

SNMP/MIB 處理

Xilinx千兆以太網系統參考設計(GSRD)是一個基于 EDK 的參考系統,能夠在基于TCP/IP的協議接口和用戶數據接口之間搭起一座高性能的橋梁。GSRD的組件具備滿足TCP/IP系統每比特和每包開銷要求的功能。

Xilinx還針對Monta Vista Linux和 Treck堆棧提供了發射性能基準。采用 Xilinx Platform Studio (XPS)微處理器庫定義的Nucleus PLUS RTOS,為采用MicroBlaze和PowerPC處理器的系統帶來了新的優勢。Nucleus PLUS RTOS尺寸很小,這意味著它能夠利用片上現有的存儲器,從而最大限度降低功耗,提高性能。此外,廣泛的中間件使得Nucleus PLUS RTOS成為RFID后端網絡的理想選擇。

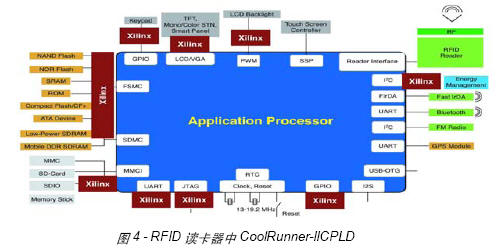

利用XilinxCoolRunnerTM-II型CPLD,手持式射頻讀卡器可連接至硬盤驅動器、QWERTY鍵盤、可移動硬盤接口、各種顯示設備和其他計算機外設(如圖4所示)。這些CPLD還能幫助應用處理器,并且滿足低功耗、高性能和更小芯片封裝等要求。

結論

將來,射頻讀卡器很可能具備前端 DSP功能,譬如射頻協議處理等。如今,這些功能在獨立式DSP中進行處理,將來,它們很有可能被集成于FPGA。嵌入式軟處理內核已可顯著提升DMIPS/MHz性能,不久以后,高版本的處理內核將取代控制讀卡器應用程序的后端外部處理器,從而借助可編程邏輯最大限度地提高射頻讀卡器設備的靈活性,同時最大限度降低其成本。

作者簡介:

Niladri Roy

Xilinx公司垂直市場營銷部ISM分部高級經理

Akshaya Trivedi

Xilinx公司垂直市場營銷部無線分部高級系統工程師

James Wong

Linear公司產品行銷經理