CPLD在射頻卡讀寫(xiě)器中的應(yīng)用

文章出處:http://www.xujuanpiju.com 作者:江美龍 于興啟 畢慧玲 沈樹(shù)群 人氣: 發(fā)表時(shí)間:2011年10月22日

1 系統(tǒng)工作原理和CPLD特性

射頻卡讀寫(xiě)系統(tǒng)又稱射頻識(shí)別系統(tǒng)(Radio Frequency Identification),它是利用無(wú)線方式進(jìn)行非接觸式雙向數(shù)據(jù)通信,進(jìn)而達(dá)到識(shí)別目標(biāo)并交換信息的目的。射頻識(shí)別技術(shù)發(fā)展迅速,在門禁、交通這、防盜、金融、身份證管理、工業(yè)自動(dòng)化等方面有著廣泛的應(yīng)用前景。按照相關(guān)標(biāo)準(zhǔn),非接觸IC卡可以分為3種:(1)密耦合卡(ISO10536),作用距離0~1cm。(2)近耦合卡(ISO 14443),作用距離0~10cm。(3)疏耦合卡(ISO 15693),作用距離0~150cm。

基于ISO 15693協(xié)議標(biāo)準(zhǔn)設(shè)計(jì)的射頻卡讀寫(xiě)器是目前中低頻段工作距離最遠(yuǎn)(達(dá)1.5米)的射頻識(shí)別裝置。射頻卡由半導(dǎo)體廠商提供,目前國(guó)內(nèi)外均有符合該標(biāo)準(zhǔn)的商用化射頻卡。

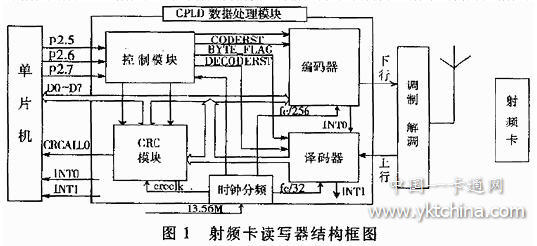

讀寫(xiě)器和射頻卡之間的數(shù)據(jù)交換主要有兩種:(1)下行數(shù)據(jù)是讀寫(xiě)器向射頻卡發(fā)送的具有固定幀格式的指令和數(shù)據(jù):(1)上行數(shù)據(jù)是射頻卡響應(yīng)讀寫(xiě)器指令后返回的數(shù)據(jù)。讀寫(xiě)器分前端收發(fā)模塊和后臺(tái)數(shù)據(jù)處理模塊。本文主要涉及數(shù)據(jù)處理部分,其主要功能有:指令裝配、下行數(shù)據(jù)編碼(讀寫(xiě)器→卡)、上行數(shù)據(jù)解碼(卡→讀寫(xiě)器)以及差錯(cuò)控制模塊。射頻卡讀寫(xiě)器結(jié)構(gòu)如圖1所示。

在實(shí)際應(yīng)用中,密耦合卡和近耦合卡距離射頻卡讀寫(xiě)器作用距離特別小,一般每次只要求響應(yīng)一張卡(如公交售票系統(tǒng))。而疏耦合卡往往應(yīng)用在對(duì)多卡同時(shí)進(jìn)行響應(yīng)的場(chǎng)合(如多個(gè)持卡行李同時(shí)經(jīng)過(guò)門檢),讀寫(xiě)器與多卡同時(shí)進(jìn)行數(shù)據(jù)交換可以通過(guò)軟件設(shè)計(jì)加入“防碰撞機(jī)制”實(shí)現(xiàn)。但是由于讀寫(xiě)器在響應(yīng)某張卡時(shí)的數(shù)據(jù)交換時(shí)間被限制在200μs~300μs內(nèi),選用普通單片機(jī)無(wú)法達(dá)到這一要求,因此在設(shè)計(jì)中選用了高速CPLD器件來(lái)實(shí)現(xiàn)編碼、解碼以及差錯(cuò)控制功能。一方面在響應(yīng)時(shí)間上滿足了實(shí)際應(yīng)用的需要;另一方面簡(jiǎn)化了軟件設(shè)計(jì)。

CPLD是從PAL和GAL發(fā)展起來(lái)陣列型高密度PLD器件,內(nèi)部由可編程邏輯宏單元、可編程I/O單元、可編程內(nèi)部連線構(gòu)成。它們大多采用E2PROM和FLASH閃存工藝,掉電后編程信息不丟失[2]。器件性能可以滿足不同場(chǎng)合的需要,如XILINX.htm" target="_blank" title="XILINX貨源和PDF資料">XILINX公司XC95XL系列CPLD具有低功耗特性,輸出電壓2.5V/3.3V,端到端延時(shí)5ns,系統(tǒng)最高工作頻率可達(dá)178M[3]。目前CPLD器件被廣泛應(yīng)用于代替中小規(guī)模數(shù)字電路,提高系統(tǒng)的可靠性、抗干擾性能和處理速度。通過(guò)管腳鎖定和預(yù)留切換端口,可以在不改動(dòng)原PCB電路板的基礎(chǔ)上對(duì)模塊的功能進(jìn)行修改和完善,給調(diào)試帶來(lái)方便。

2 功能模塊實(shí)現(xiàn)

2.1 編碼器與譯碼器

單片機(jī)啟動(dòng)編碼后,編碼模塊向單片機(jī)發(fā)中斷(INT0)獲取待編碼的指令數(shù)據(jù),同時(shí)將指令數(shù)據(jù)送入并行CRC模塊。當(dāng)指令數(shù)據(jù)完成編碼后,控制電路將2字節(jié)CRC值緊接在數(shù)據(jù)之后進(jìn)行編碼。譯碼時(shí),譯碼器檢測(cè)到起始位后,開(kāi)始譯碼。譯碼后的數(shù)據(jù)通過(guò)中斷(INT1)通知單片機(jī)取走。并同時(shí)送入CRC并行運(yùn)算模塊進(jìn)行校驗(yàn),單片機(jī)在特定的時(shí)刻(接收完最后一字節(jié)數(shù)據(jù)時(shí))讀取CRC校驗(yàn)標(biāo)志端口CRCALL0,判斷整個(gè)數(shù)據(jù)串的正確性。

編譯碼的數(shù)據(jù)格式如下:

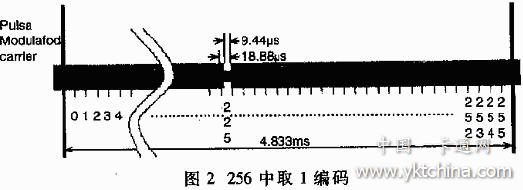

(1)數(shù)據(jù)編碼 從讀寫(xiě)器到卡的數(shù)據(jù)采用脈沖位置調(diào)制即“1/256”編碼。用256個(gè)時(shí)隙表示8bit數(shù)據(jù),通過(guò)控制bit脈沖出現(xiàn)的時(shí)間位置來(lái)表示0~255范圍內(nèi)的數(shù)據(jù)。如圖2,在第255個(gè)位置出現(xiàn)的位置脈沖(9.44μs高電平的9.44μs低電平)表示數(shù)據(jù)E1(HEX),采用計(jì)數(shù)器加控制電路即可實(shí)現(xiàn)。控制部分協(xié)助實(shí)現(xiàn)數(shù)據(jù)無(wú)縫編碼及形成幀起始位和結(jié)束位,用VHDL設(shè)計(jì)易于實(shí)現(xiàn)。編碼后的數(shù)據(jù)進(jìn)行ASK調(diào)制(13.56MHz載波),經(jīng)天線發(fā)射出去。

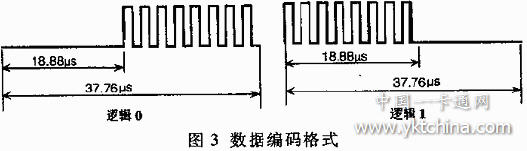

(2)數(shù)據(jù)譯碼 從射頻卡返回的數(shù)據(jù)經(jīng)過(guò)一次解調(diào)(去掉13.56MHz載波)后,數(shù)據(jù)編碼格式如圖3所示。可以直接進(jìn)行數(shù)據(jù)譯碼,也可以去除子載波(423.75kHz)后得到Manchester碼再譯碼。這里采用后者,通過(guò)在每一bit的前、后半段時(shí)間內(nèi)兩次取樣、判決、加以串并變換即可得到譯碼后的并行數(shù)據(jù)并送至并行CRC模塊進(jìn)行CRC校驗(yàn),同時(shí)送往單片機(jī)處理,行CRC模塊在校驗(yàn)結(jié)束時(shí)通知單片機(jī)取校驗(yàn)結(jié)果。

2.2 差錯(cuò)處理模塊

與射頻卡內(nèi)部電路配合,讀寫(xiě)器端采用了常用的CRC檢錯(cuò)得傳機(jī)制。為了縮短處理時(shí)間,滿足讀寫(xiě)器在實(shí)際應(yīng)用中對(duì)多張卡同時(shí)處理時(shí)的響應(yīng)時(shí)間要求,設(shè)計(jì)采用硬件實(shí)現(xiàn)。

計(jì)算下行數(shù)據(jù)的CRC值以及對(duì)上行數(shù)據(jù)進(jìn)行CRC校驗(yàn),實(shí)際上都是完成數(shù)據(jù)的CRC計(jì)算,二者可以共用一個(gè)模塊,通過(guò)控制部分協(xié)調(diào)分工。通常CRC采用性反饋移位寄存器串行實(shí)現(xiàn)(見(jiàn)圖4),這里提出了一種并行計(jì)算CRC的方法,具有更高的處理速度,使讀寫(xiě)器對(duì)響應(yīng)時(shí)間縮短。

CRC-CCITT算法生成多相式為:x 16+x 12+x 5+1[4]。計(jì)算CRC實(shí)際上是將數(shù)據(jù)通過(guò)線性反饋移位寄存器,所有數(shù)據(jù)移入后CRC寄存器的值即為16位CRC值。并行CRC運(yùn)算模塊每次輸入8位數(shù)據(jù),相當(dāng)于一次并行運(yùn)算就得到了串行移位運(yùn)算時(shí)需要8位移位所得的結(jié)束。由表1~表4可以知道并行CRC實(shí)現(xiàn)的原理:每個(gè)時(shí)鐘到來(lái)時(shí)完成8bit數(shù)據(jù)CRC值計(jì)算;下一個(gè)8bit數(shù)據(jù)到來(lái)時(shí),把上一個(gè)8bit數(shù)據(jù)的CRC值C15~C0作為初值,繼續(xù)完成并行CRC計(jì)算。即每次處理一個(gè)字節(jié)。

表1 移位前CRC寄存器值(初值)

| R15 | R14 | R13 | R12 | R11 | R10 | R9 | R8 | R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 |

| C15 | C14 | C13 | C12 | C11 | C10 | C9 | C8 | C7 | C6 | C5 | C4 | C3 | C2 | C1 | C0 |

表2 1次移位后CRC寄存器值

| R15 | R14 | R13 | R12 | R11 | R10 | R9 | R8 | R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 |

| X0 | C15 | C14 | C13 | C12 | C11 X0 |

C10 | C9 | C8 | C7 | C6 | C5 | C4 X0 |

C3 | C2 | C1 |

表3 2次移位后CRC寄存器

| R15 | R14 | R13 | R12 | R11 | R10 | R9 | R8 | R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 |

| X1 | X0 | C15 | C14 | C13 | C12 X1 |

C11 X0 |

C10 | C9 | C8 | C7 | C6 | C5 X1 |

C4 X0 |

C3 | C2 |

表4 8次移位后CRC寄存器值

| R15 | R14 | R13 | R12 | R11 | R10 | R9 | R8 | R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 |

| X7 X3 |

X6 X2 |

X5 X1 |

X4 X0 |

X3 | X7 X2 |

X6 X1 |

X5 X0 |

C15 X4 |

C14 X3 |

C13 X2 |

C12 X1 |

C11 X7 X0 |

C10 X6 |

C9 X5 |

C8 X4 |

表中參數(shù)說(shuō)明:Ri為CRC移位寄存器值(R0為低位),Ci為CRC移位寄存器初值(C0為低位),Di為輸入數(shù)據(jù)(D0為低位),Xi=Di XDR Ci,同一欄中數(shù)據(jù)的運(yùn)算關(guān)系是異或(XOR)。

每次并行數(shù)據(jù)到來(lái)時(shí),各CRC寄存器值按表4運(yùn)算關(guān)系更新。最后一個(gè)字節(jié)數(shù)據(jù)輸入后CRC寄存器的值(R0~R15)即為該數(shù)據(jù)組的CRC值。模塊設(shè)計(jì)采用了VHDL語(yǔ)言,同步更新R0~R15寄存器的值,從表中看出,一次CRC計(jì)算最多完成4組XOR運(yùn)算。如:R3<=C11 XOFR D7 XOR C7 XOR D0 XOR X0;R15<=D7XOR C7 XOR D3 XOR C3。

3 控制模塊

單片機(jī)擴(kuò)展了RAM后,P2口只有P2.5~P2.7可以用來(lái)提供控制信號(hào),不能滿足需要,因而在CPLD內(nèi)部將3路信號(hào)擴(kuò)展為8路控制信號(hào),以實(shí)現(xiàn)對(duì)各部分進(jìn)行協(xié)調(diào)控制。主要有編碼器和譯碼器的啟動(dòng)信號(hào)、復(fù)位信號(hào)、指令標(biāo)志信號(hào)、CRC輸出信號(hào)等控制信號(hào)。

4 性能分析

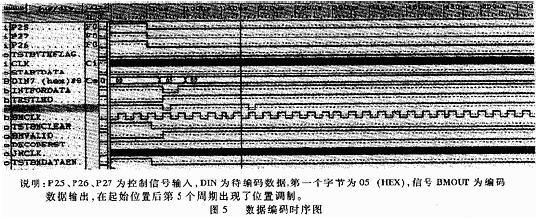

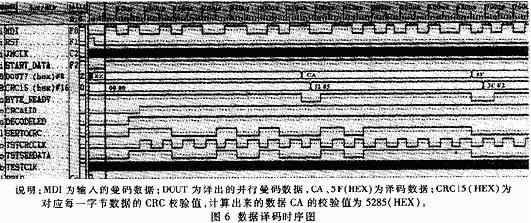

這里選用1片XILINX XC95144實(shí)現(xiàn)整個(gè)數(shù)據(jù)處理模塊的功能,使用軟件平臺(tái)是XILINX.htm" target="_blank" title="XILINX貨源和PDF資料">XILINX Foundation 3.1i。XC95144內(nèi)部有144個(gè)宏單元、3200可用門。圖5和圖6分別給出了編碼器和譯碼器的部分時(shí)序仿真結(jié)果及其說(shuō)明。可以看到,二者均實(shí)現(xiàn)了協(xié)議要求,編碼器在準(zhǔn)確的位置實(shí)現(xiàn)脈沖位置調(diào)制,譯碼器能準(zhǔn)確地對(duì)曼徹斯特碼數(shù)據(jù)進(jìn)行譯碼,并計(jì)算出輸入數(shù)據(jù)的CRC值。

用AT89C51單片機(jī)提供編碼數(shù)據(jù)以及模擬待譯碼曼碼數(shù)據(jù)流對(duì)模塊功能進(jìn)行實(shí)測(cè),用示波器觀察各測(cè)試點(diǎn)信號(hào),結(jié)果基本上與時(shí)序仿真的波形圖相同,達(dá)到了預(yù)期設(shè)計(jì)的目標(biāo)。

本文較系統(tǒng)地介紹了一類遠(yuǎn)距離射頻卡讀寫(xiě)器數(shù)字處理模塊的設(shè)計(jì),特別在于:(1)采用單片CPLD實(shí)現(xiàn)了射頻卡讀寫(xiě)器數(shù)字模塊功能,采用了原理圖和VHDL相結(jié)合自頂向下的設(shè)計(jì)方法[2][5],樣機(jī)PCB版面積小,開(kāi)發(fā)周期短,性能穩(wěn)定。其設(shè)計(jì)方案和思路對(duì)其他類別射頻卡讀寫(xiě)器設(shè)計(jì)具有一定的參考價(jià)值。(2)提出了一種快速實(shí)現(xiàn)CRC-CCITT的并行運(yùn)算方法,該方法適用于高速數(shù)據(jù)傳輸場(chǎng)合。

為了提高系統(tǒng)的安全性,可以對(duì)對(duì)寫(xiě)入卡中的數(shù)據(jù)進(jìn)行加密處理,即引入數(shù)據(jù)加密模塊,并將整個(gè)設(shè)計(jì)配置到一片容量更大的CPLD或FPGA中。

作者:北京郵電大學(xué)電子工程學(xué)院智能信息處理實(shí)驗(yàn)室(100876)江美龍 于興啟 畢慧玲 沈樹(shù)群